- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Lapisan Epitaxial: Asas Peranti Semikonduktor Termaju

Rajah 1: Menggambarkan korelasi antara kepekatan doping, ketebalan lapisan dan voltan pecahan untuk peranti unipolar.

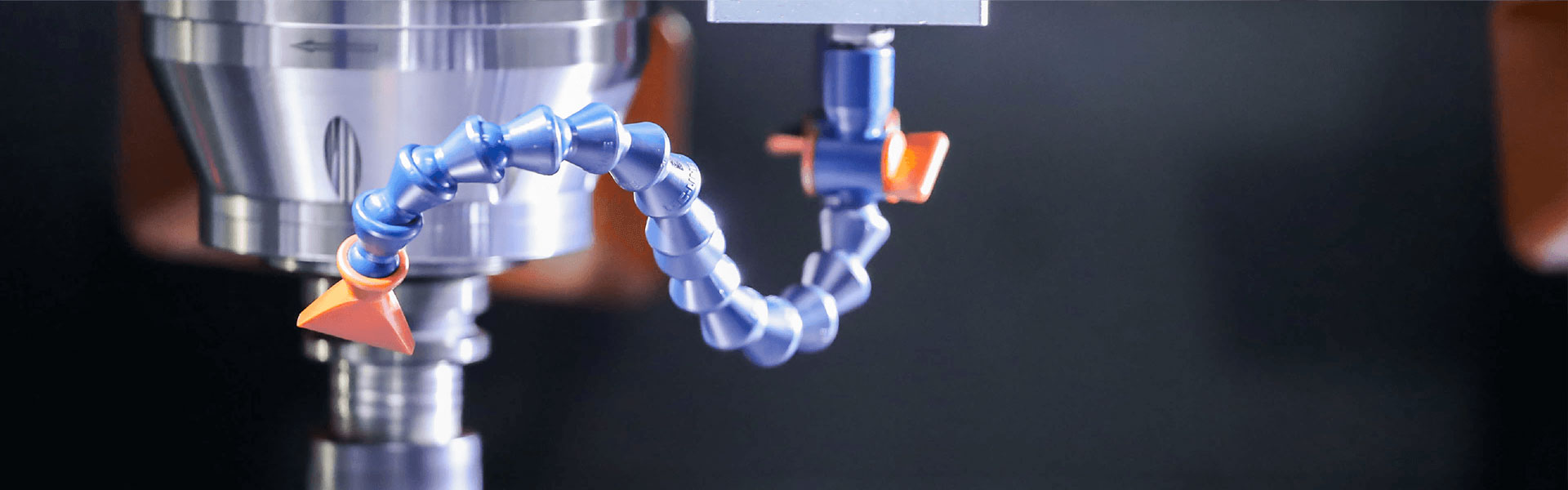

Penyediaan lapisan epitaxial SiC terutamanya merangkumi teknik seperti Pertumbuhan Sejatan, Epitaksi Fasa Cecair (LPE), Epitaksi Rasuk Molekul (MBE), dan Pemendapan Wap Kimia (CVD), dengan CVD menjadi kaedah utama untuk pengeluaran besar-besaran di kilang.

Jadual 1: Menyediakan gambaran keseluruhan perbandingan kaedah penyediaan lapisan epitaxial utama.

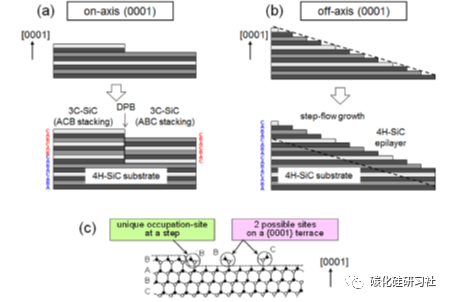

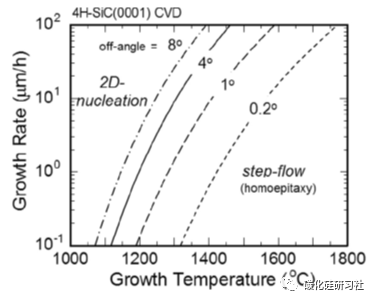

Pendekatan terobosan melibatkan pertumbuhan pada substrat luar paksi {0001} pada sudut kecondongan tertentu, seperti yang digambarkan dalam Rajah 2(b). Kaedah ini meningkatkan ketumpatan langkah dengan ketara sambil mengurangkan saiz langkah, memudahkan nukleasi terutamanya di tapak tandan langkah dan dengan itu, membolehkan lapisan epitaxial meniru dengan sempurna urutan susunan substrat, menghapuskan kewujudan bersama politaip.

Rajah 2: Menunjukkan proses fizikal epitaksi terkawal langkah dalam 4H-SiC.

Rajah 3: Menunjukkan keadaan kritikal untuk pertumbuhan CVD dalam epitaksi terkawal langkah untuk 4H-SiC.

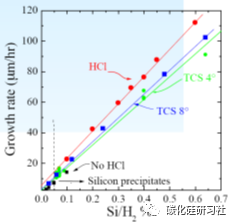

Rajah 4: Membandingkan kadar pertumbuhan di bawah sumber silikon yang berbeza untuk epitaksi 4H-SiC.

Dalam bidang aplikasi voltan rendah dan sederhana (mis., peranti 1200V), teknologi epitaksi SiC telah mencapai tahap matang, menawarkan keseragaman yang agak unggul dalam ketebalan, kepekatan doping, dan pengagihan kecacatan, memenuhi keperluan untuk SBD voltan rendah dan sederhana dengan secukupnya. , MOS, peranti JBS dan lain-lain.

Walau bagaimanapun, domain voltan tinggi masih memberikan cabaran yang ketara. Sebagai contoh, peranti yang dinilai pada 10000V memerlukan lapisan epitaxial kira-kira 100μm tebal, tetapi lapisan ini mempamerkan ketebalan dan keseragaman doping yang jauh lebih lemah berbanding dengan rakan sejawatan voltan rendah mereka, apatah lagi kesan buruk kecacatan segi tiga pada prestasi keseluruhan peranti. Aplikasi voltan tinggi, yang cenderung memihak kepada peranti bipolar, juga meletakkan permintaan yang ketat pada hayat pembawa minoriti, memerlukan pengoptimuman proses untuk meningkatkan parameter ini.

Pada masa ini, pasaran dikuasai oleh wafer epitaxial SiC 4 inci dan 6 inci, dengan peningkatan beransur-ansur dalam bahagian wafer epitaxial SiC berdiameter besar. Saiz wafer epitaxial SiC secara asasnya ditentukan oleh dimensi substrat SiC. Dengan substrat SiC 6-inci kini tersedia secara komersil, peralihan daripada epitaksi SiC 4-inci kepada 6-inci sedang dijalankan secara berterusan.

Apabila teknologi fabrikasi substrat SiC berkembang dan kapasiti pengeluaran berkembang, kos substrat SiC semakin berkurangan. Memandangkan substrat menyumbang lebih daripada 50% daripada kos wafer epitaxial, penurunan harga substrat dijangka membawa kepada kos yang lebih rendah untuk epitaksi SiC, sekali gus menjanjikan masa depan yang lebih cerah untuk industri.**